RESM

Raw Execution Step Machine

also known as Bit Bit Jump Jump machine (BBJJ) — a minimal computer with a single uniform instruction type

The One Instruction

RESM is a minimal computer design built around a single, uniform instruction type. Every program — no matter how complex — is composed entirely of repetitions of this one instruction. There are no other opcodes. No special cases.

PPS = Program Path Selector — a single bit in RAM that determines branching. Writing to address 0x02 sets PPS as a side effect of COPY_TO.

Every instruction executes in exactly three phases:

Fetch the bit at the address given by COPY_FROM.

Write the fetched bit to the address given by COPY_TO. This may update PPS.

If PPS = 0, set IP ← IP_CASE_0. If PPS = 1, set IP ← IP_CASE_1.

The machine has no concept of "word size" — it operates on individual bits. Words of any width (8-bit, 16-bit, arbitrary) are constructed from sequences of instructions. This is not a limitation: it is the source of the design's expressive uniformity.

The machine is Turing complete: any computation expressible in any other Turing-complete system can be expressed in RESM. This has been demonstrated through implemented programs — see the Programs section below.

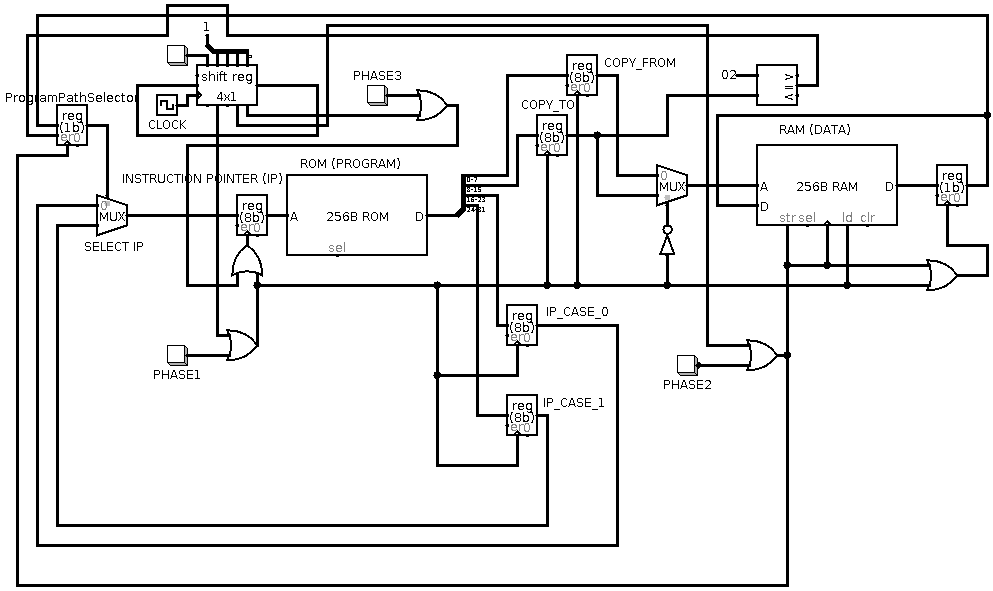

Circuit Implementation (Logisim)

RESM has been implemented as a simulable circuit using Logisim. The schematic is fully interactive: you can load it and step through instruction execution to watch the machine operate at the gate level.

Click the image to open full resolution. Download the full Logisim project and Violet flowcharts from the repo archive.

HW Design notes

Because every instruction has the same structure and takes the same number of phases, multi-core extensions are straightforward: cores share phase-timing signals and stay naturally synchronized. I/O is handled by designating special memory addresses as input and output ports — no separate I/O instructions are needed.

The uniform instruction set also makes RESM a natural candidate for FPGA implementation, where the RESM microcode would serve as the programming layer above the native FPGA toolchain. Flowchart diagrams for programs are provided in Violet format.

Virtual Machine Implementations

Three independent VM implementations exist for RESM — in JavaScript, Python, and Java. All three execute the same instruction semantics. Their convergence on identical outputs for the same programs constitutes a cross-verification of the specification.

In-browser interpreter using standard web APIs. Zero installation. Includes a raw assembler for writing programs. The most accessible entry point to RESM.

▶ Live demo → GitHub: copyjump.js

Parses human-readable .prg.txt files.

Hosts the most complex program written for RESM to date:

byte addition with carry output — written by hand, no compiler.

Parses binary .cj format

and converts from .prg.txt.

Ships with a runnable demo: integer_counter.cj.

Program file formats

Two formats exist for encoding RESM programs.

.prg.txt is the textual, human-readable format (used in Python VM).

.cj is the numeric binary format (used in Java VM).

The Java VM includes a converter between the two.

Demonstrated Programs

All programs below were written directly in RESM instruction format — no compiler used, only a text editor (for the textual format) or the raw assembler (for the JS version). Each program demonstrates a class of computation emergent from COPY + JUMP alone.

| Program | Domain | Notes |

|---|---|---|

| NOT gate | Boolean logic | Logical negation derived from COPY+JUMP. Flowchart in Violet. |

| OR gate | Boolean logic | Two-input OR. Demonstrates conditional path selection as logic gate. Flowchart in Violet. |

| Integer counter 0→255 | Arithmetic |

Counts a byte from 0 to 255 continuously.

Runnable as integer_counter.cj in the Java VM.

quick demo

|

| Byte addition with carry | Arithmetic | Sums 2 input bytes → 1 output byte + 1 carry bit. Most complex program written for RESM to date. Written entirely by hand. most complex |

From NOT and OR gates, all of Boolean algebra (AND, XOR, NAND…) follows by composition. From addition follows all arithmetic. The ladder from gates to full computation is concretely walkable within RESM — no new instruction types needed at any rung.

The Central Demonstration

The Logisim circuit (HW) and the three VMs (SW) are independent implementations of the same specification. When run on the same programs, they produce identical outputs. This convergence demonstrates that the RESM semantics are well-defined and implementation-independent — not an artifact of any single language or simulator.

This is the core claim of RESM as a minimal computer design: not just that the instruction set is small, but that the specification is precise enough to be independently realized in hardware and in multiple software environments, and that these realizations agree.

The byte addition with carry program — written by hand in a text editor, executed by the Python VM and by the Logisim circuit — is the sharpest existing demonstration of this convergence.

Background Articles

Three articles on arkenidar.com/wordpress provide the conceptual and historical framing: